Datumcentra migrado al DDR5 povas esti pli grava ol aliaj ĝisdatigoj.Tamen multaj homoj nur malklare pensas, ke DDR5 estas nur transiro por tute anstataŭigi DDR4.Procesoroj neeviteble ŝanĝiĝas kun la alveno de DDR5, kaj ili havos kelkajn novajnmemorointerfacoj, kiel estis la kazo kun antaŭaj generacioj de DRAM-ĝisdatigaĵoj de SDRAM ĝisDDR4.

Tamen, DDR5 ne estas nur interfaca ŝanĝo, ĝi ŝanĝas la koncepton de procesora memorsistemo.Fakte, la ŝanĝoj al DDR5 eble sufiĉas por pravigi ĝisdatigon al kongrua servila platformo.

Kial elekti novan memorinterfacon?

Komputilproblemoj kreskis pli kompleksaj ekde la apero de komputiloj, kaj tiu neevitebla kresko pelis evoluon en la formo de pli granda nombro da serviloj, ĉiam kreskanta memoro kaj stokado-kapacitoj, kaj pli altaj procesoraj horloĝrapidoj kaj kernkalkuloj, sed ankaŭ kondukante arkitekturajn ŝanĝojn. , inkluzive de la lastatempa adopto de disigitaj kaj efektivigitaj AI-teknikoj.

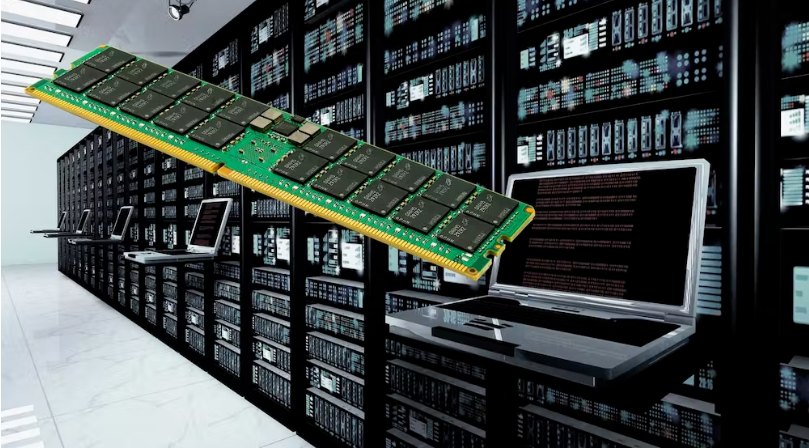

Iuj povus pensi, ke ĉi tiuj ĉiuj okazas en tandemo ĉar ĉiuj nombroj pliiĝas.Tamen, dum la nombro da procesoraj kernoj pliiĝis, DDR-bendolarĝo ne daŭrigis, do la bendolarĝo per kerno efektive malpliiĝis.

Ĉar datumaj aroj disetendiĝis, precipe por HPC, ludoj, videokodigado, maŝinlernada rezonado, analizo de grandaj datumoj kaj datumbazoj, kvankam la bendolarĝo de memortranslokigoj povas esti plibonigita aldonante pli da memorkanaloj al la CPU, Sed ĉi tio konsumas pli da potenco. .La procesoro-pingla nombro ankaŭ limigas la daŭripovon de ĉi tiu aliro, kaj la nombro da kanaloj ne povas pliiĝi eterne.

Kelkaj aplikoj, precipe altkernaj subsistemoj kiel ekzemple GPUoj kaj specialecaj AI-procesoroj, uzas specon de alt-bendolarĝa memoro (HBM).La teknologio kuras datumojn de stakitaj DRAM-fritoj al la procesoro tra 1024-bitaj memorvojoj, igante ĝin bonega solvo por memorintensaj aplikoj kiel AI.En ĉi tiuj aplikoj, la procesoro kaj memoro devas esti kiel eble plej proksimaj por disponigi rapidajn translokigojn.Tamen, ĝi ankaŭ estas pli multekosta, kaj la blatoj ne povas konveni sur anstataŭigeblaj/ĝisdatigeblaj moduloj.

Kaj DDR5-memoro, kiu komencis esti vaste lanĉita ĉi-jare, estas desegnita por plibonigi la kanalan bendolarĝon inter la procesoro kaj la memoro, samtempe subtenante ĝisdatigeblecon.

Bandwidth kaj latencia

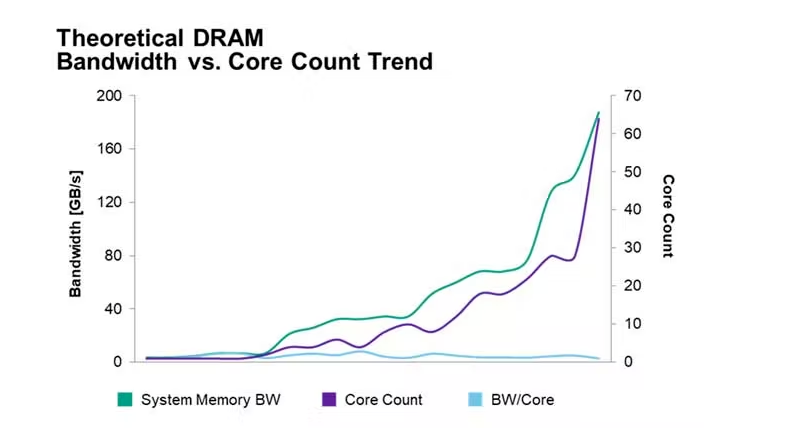

La transiga indico de DDR5 estas pli rapida ol tiu de ajna antaŭa generacio de DDR, fakte, kompare kun DDR4, la transiga indico de DDR5 estas pli ol duobla.DDR5 ankaŭ enkondukas pliajn arkitekturajn ŝanĝojn por ebligi agadon ĉe ĉi tiuj transigaj tarifoj super simplaj gajnoj kaj plibonigos la observitan datumbusan efikecon.

Plie, la krevlongo estis duobligita de BL8 ĝis BL16, permesante al ĉiu modulo havi du sendependajn sub-kanalojn kaj esence duobligante la disponeblajn kanalojn en la sistemo.Vi ne nur ricevas pli altajn transigajn rapidojn, sed vi ankaŭ ricevas rekonstruitan memorkanalon, kiu superas DDR4 eĉ sen pli altaj transigaj tarifoj.

Memorintensaj procezoj vidos grandegan akcelon de la transiro al DDR5, kaj multaj el la hodiaŭaj datumintensaj laborŝarĝoj, precipe AI, datumbazoj kaj interreta transakcia prilaborado (OLTP), taŭgas ĉi tiun priskribon.

La transdona indico ankaŭ estas tre grava.La nuna rapidintervalo de DDR5-memoro estas 4800~6400MT/s.Dum la teknologio maturiĝas, la dissendrapideco estas atendita esti pli alta.

Energia konsumo

DDR5 uzas pli malaltan tension ol DDR4, te 1.1V anstataŭ 1.2V.Dum diferenco de 8% eble ne sonas kiel multe, la diferenco evidentiĝas kiam ili estas kvadratitaj por kalkuli la elektrokonsuman rilatumon, te 1,1²/1,2² = 85%, kio tradukiĝas al 15% ŝparado en elektrofakturoj.

La arkitekturaj ŝanĝoj enkondukitaj de DDR5 optimumigas bendolarĝan efikecon kaj pli altajn transigajn tarifojn, tamen, ĉi tiuj nombroj malfacilas kvantigi sen mezuri la ĝustan aplikaĵan medion en kiu la teknologio estas uzata.Sed denove, pro la plibonigita arkitekturo kaj pli altaj transigaj tarifoj, la finuzanto perceptos plibonigon de energio por peco da datumoj.

Krome, la DIMM-modulo ankaŭ povas ĝustigi la tension per si mem, kio povas redukti la bezonon de alĝustigo de la nutrado de la ĉeftabulo, tiel provizante pliajn energiŝparajn efikojn.

Por datumcentroj, kiom da potenco konsumas servilo kaj kiom da malvarmigokostoj estas zorgoj, kaj kiam ĉi tiuj faktoroj estas konsiderataj, DDR5 kiel pli energi-efika modulo certe povas esti kialo por ĝisdatigi.

Korekto de eraro

DDR5 ankaŭ inkluzivas sur-blatan erarĝustigon, kaj ĉar DRAM-procezoj daŭre ŝrumpas, multaj uzantoj zorgas pri pliigado de la unubit-erara indico kaj ĝenerala datuma integreco.

Por servilaj aplikoj, sur-blato ECC korektas unubitajn erarojn dum legaj komandoj antaŭ eligo de datumoj de DDR5.Ĉi tio malŝarĝas iom da la ECC-ŝarĝo de la sistema korekta algoritmo al DRAM por redukti la ŝarĝon sur la sistemo.

DDR5 ankaŭ enkondukas erarkontroladon kaj sanigon, kaj se ebligita, DRAM-aparatoj legos internajn datumojn kaj reskribos korektitajn datumojn.

Resumu

Dum la DRAM-interfaco kutime ne estas la unua faktoro kiun datumcentro konsideras kiam efektivigas ĝisdatigon, DDR5 meritas pli detale rigardon, ĉar la teknologio promesas ŝpari potencon dum multe plibonigas rendimenton.

DDR5 estas ebliga teknologio, kiu helpas fruajn adoptantojn migri gracie al la komponebla, skalebla datumcentro de la estonteco.IT kaj komercaj gvidantoj devus taksi DDR5 kaj determini kiel kaj kiam migri de DDR4 al DDR5 por kompletigi siajn datumcentrajn transformplanojn.

Afiŝtempo: Dec-15-2022